#### Instruction scheduling

Michel Schinz Advanced compiler construction – 2008-05-30

#### Instruction ordering

When a compiler emits the instructions corresponding to a program, it imposes a total order on them.

However, that order is usually not the only valid one, in the sense that it can be changed without modifying the program's behaviour.

For example, if two instructions  $i_1$  and  $i_2$  appear sequentially in that order and are independent, then it is possible to swap them.

#### Instruction scheduling

Among all the valid permutations of the instructions composing a program – *i.e.* those that preserve the program's behaviour – some can be more desirable than others. For example, one order might lead to a faster program on some machine, because of architectural constraints.

The aim of **instruction scheduling** is to find a valid order that optimises some metric, like execution speed.

## Pipeline stalls

Modern, pipelined architectures can usually issue at least one instruction per clock cycle.

However, an instruction can be executed only if the data it needs is ready. Otherwise, the pipeline **stalls** for one or several cycles.

Stalls can appear because some instructions (e.g. division) require several cycles to complete, or because data has to be fetched from memory.

#### Scheduling example Scheduling example The following example will illustrate how proper scheduling Instruction Instruction Cycle Cycle can reduce the time required to execute a piece of code. 1 LOAD R1 R30 0 110AD R1 R30 0 To simplify the examples, we assume that LOAD and STOR instructions accept a constant as third argument. 4 ADD R1 R1 R1 2 LOAD R2 R30 1 5 LOAD R2 R30 1 3 LOAD R3 R30 2 Moreover, we assume the following delays for instructions: 8 MUL R1 R1 R2 4 ADD R1 R1 R1 Instruction(s) Delay 9 LOAD R2 R30 2 5 MUL R1 R1 R2 LOAD, STOR 3 12 MUL R1 R1 R2 6 LOAD R2 R30 3 MUL 2 13 LOAD R2 R30 3 7 MUL R1 R1 R3 16 MUL R1 R1 R2 ADD 1 9 MUL R1 R1 R2 18 STOR R1 R30 4 11 STOR R1 R30 4 After scheduling (including renaming), the last instruction is issued at cycle 11 instead of 18!

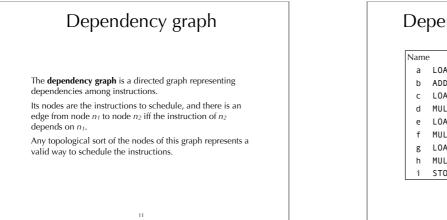

#### Instruction dependencies

An instruction  $i_2$  **depends** on an instruction  $i_1$  when it is not possible to execute  $i_2$  before  $i_1$  without changing the behaviour of the program.

The most common reason for dependency is datadependency:  $i_2$  uses a value that is computed by  $i_1$ . However, as we will see, there are other kinds of dependencies.

#### Data dependencies

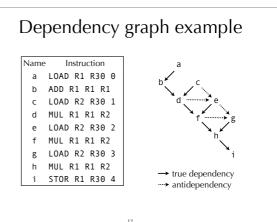

We distinguish three kinds of dependencies between two instructions  $i_1$  and  $i_2$ :

- true dependency *i*<sub>2</sub> reads a value written by *i*<sub>1</sub> (read after write, RAW),

- anti-dependency *i*<sub>2</sub> writes a value read by *i*<sub>1</sub> (write after read, WAR),

- anti-dependency *i*<sub>2</sub> writes a value written by *i*<sub>1</sub> (write after write, WAW).

# Anti-dependencies

Anti-dependencies are not real dependencies, in the sense that they do not arise from the flow of data. They are due to a single location - e.g. a register - being used to store different values.

Most of the time, anti-dependencies can be removed by renaming locations – e.g. registers.

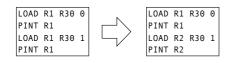

In the example below, the program on the left contains a WAW anti-dependency between the two LOAD instructions, that can be removed by renaming the second use of R1.

#### Difficulty of scheduling

Optimal instruction scheduling is NP-complete.

As always, this implies that we will use techniques based on heuristics to find a good – but sometimes not optimal – solution to that problem.

**List scheduling** is a technique to schedule the instructions of *a single basic block*.

Its basic idea is to simulate the execution of the instructions, and to try to schedule instructions only when all their operands can be used without stalling the pipeline.

13

## List scheduling algorithm

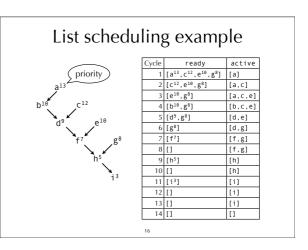

The list scheduling algorithm maintains two lists:

- ready is the list of instructions that could be scheduled without stall, ordered by priority,

- active is the list of instructions that are being executed.

At each step, the highest-priority instruction from ready is scheduled, and moved to active, where it stays for a time equal to its delay.

14

#### Scheduling conflicts **Summary** It is hard to decide whether scheduling should be done Instruction scheduling tries to find an order in which before or after register allocation. instructions should be issued to improve some metric -If register allocation is done first, it can introduce antitypically execution time. dependencies when reusing registers. List scheduling is an instruction scheduling technique. It If scheduling is done first, register allocation can introduce works by always scheduling the next instruction that is ready, spilling code, destroying the schedule. i.e. whose operands are available. When several candidate instructions exist, a heuristic is used to decide which one to Solution: schedule first, then allocate registers and schedule schedule next. once more if spilling was necessary. 17 18